Journal of the European Ceramic Society 23 (2003) 2711-2715

www.elsevier.com/locate/jeurceramsoc

# Microwave properties of SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ heterostructure on low-resistivity silicon

A. Vorobiev<sup>a,b,\*</sup>, P. Rundqvist<sup>a</sup>, K. Khamchane<sup>c</sup>, S. Gevorgian<sup>a</sup>

<sup>a</sup>Department of Microelectronics, Chalmers University of Technology, SE-41296 Göteborg, Sweden

<sup>b</sup>Institute for Physics of Microstructures RAS, N. Novgorod, GSP-105, 603600, Russia

<sup>c</sup>Department of Microelectronics and Nanoscience, Chalmers University of Technology and Göteborgs University, SE-41296 Göteborg, Sweden

#### Abstract

Properties of thin film SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ heterostructures on low-resistivity (25 Ωcm) Si substrates are studied at microwave frequencies. Heterostructures are grown by laser ablation at different conditions and characterized by XRD. Coplanar capacitors with 2 μm gap are formed by a lift-off process of the Au/Ti electrodes deposited by e-beam evaporation on the surface of heterostructures. Microwave properties of the capacitors are measured at room temperature in the range of 1–50 GHz as a function of electric field. The measured tunability of the capacitors is in the range of 10–20%. The loss in capacitors is caused mainly by the Si substrate with maximum value around the dielectric relaxation frequency 6 GHz. The intrinsic loss tangent (0.08 at 50 GHz) of capacitors is calculated from equivalent circuit model by removing the substrate loss.

Keywords: Capacitors; Dielectric properties; SrTiO<sub>3</sub>

# 1. Introduction

Strontium-titanate, SrTiO<sub>3</sub> (STO), or a solid solution of Ba<sub>1-x</sub>Sr<sub>x</sub>TiO<sub>3</sub> (BSTO), are being investigated as dielectric material for tunable microwave applications. 1-4 The electric field-dependent dielectric permittivity can be utilized in devices such as varactors, tunable oscillators, phase shifters, etc. 1,5,6 Usually these devices require high tunability of permittivity and low dielectric loss. It is important, from an industrial respective, to integrate these devices with the Si substrate since microwave ICs are going to heavily rely on Si technology. However, the resistivity of common CMOS grade silicon wafers is rather low (in the range of  $1-25 \Omega$  cm) that causes high microwave loss in circuit elements placed directly on Si substrates. A number of methods have been developed to solve this problem. The first approach is to use commercially available high resistive Si wafers (up to 10 k $\Omega$  cm) since all circuit components may be implemented in the same way as they are on semi-insulating GaAs, InP, or ceramic substrates.<sup>4,7</sup> Another approach is to form the circuit elements directly on low resistivity Si and then to remove

E-mail address: andrei.vorobyev@ep.chalmers.se (A. Vorobiev).

the Si areas below the elements using micromachining techniques.<sup>8</sup>

In this paper we present the results of preparation and the microwave study of a heterostructure, incorporating STO thin film, on low resistivity Si ( $\rho$ =25  $\Omega$  cm). In order to provide the epitaxial growth and improved dielectric properties of STO layer we grew a SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ buffer thin film structure between STO and the Si substrate. <sup>9,10,11</sup>

# 2. Experimental

# 2.1. Sample preparation

The SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ and CeO<sub>2</sub>/YSZ heterostructures were grown in situ by pulsed laser deposition technique on n-type Si(100) substrates ( $\rho$ =25  $\Omega$  cm) with native SiO<sub>2</sub> layer. A beam of KrF excimer laser ( $\lambda$ =248 nm,  $\tau$ =30 ns) operating at 10 Hz with energy density of 1.5 J cm<sup>-2</sup> was used to ablate the stoichiometric targets. An on-axis deposition configuration with target-to-substrate distance of 5 cm was used. The substrates are fixed to the surface of resistive heater with silver glue. The growth temperature of each layer was optimized for crystal quality of STO layer (intensity

<sup>\*</sup> Corresponding author.

and rocking curve of XRD  $\omega$ -scans). The growth temperature, thickness of layers and bulk lattice parameters of materials are presented in Table 1. In order to avoid further growth of the SiO<sub>2</sub> on the Si wafer, no oxygen was introduced into the vacuum chamber during the deposition of the first YSZ buffer layer. <sup>9,12</sup> The oxygen pressure during deposition of CeO<sub>2</sub>, SrRuO<sub>3</sub> and STO layers was 0.4 mbar. After deposition, the samples were cold down to room temperature at oxygen pressure of 400 mbar.

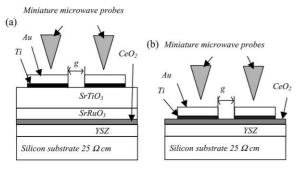

Coplanar capacitor SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ test structures were formed by a lift-off process of e-beam evaporated Au (≈0.5 µm)/Ti ( 20 nm) film electrodes. The cross section view of a capacitor test structure presented in Fig. 1(a). The electrodes have rectangular shape with lateral sizes of  $150 \times 125 \mu m^2$ . The straight gap (g) between electrodes is 2 μm. The planar design (Refs. 1, 3 and 7) used in this work is simple in fabrication, on-wafer characterization and suitable for integration with microwave integrated circuits. The SrRuO<sub>3</sub> layer is rather thin (50 nm) and its sheet resistance is high (50  $\Omega$ /square). For this reason the microwave field penetrates the silicon substrate and experiences some losses. Special CeO<sub>2</sub>/YSZ open structure with identical geometry of electrodes were fabricated and used for measurement of the losses associated with the silicon substrate. The cross sectional view of a capacitor open structure is presented in Fig. 1(b).

#### 2.2. Sample characterization

The microstructure of the layers were characterized by normal  $\theta$ -2 $\theta$  and  $\omega$ -scan XRD patterns measured

Table 1 Growth temperature  $T_d$ , thickness t of layers and bulk lattice parameters of materials a

| Layer                     | YSZ       | $CeO_2$   | $SrRuO_3$ | SrTiO <sub>3</sub> |

|---------------------------|-----------|-----------|-----------|--------------------|

| T <sub>d</sub> , °C t, nm | 770<br>50 | 720<br>10 | 780<br>50 | 700<br>100         |

| a, nm                     | 0.514     | 0.541     | 0.393     | 0.3905             |

Fig. 1. Cross section view of a capacitor SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ/Si test structure (a) and CeO<sub>2</sub>/YSZ/Si open structure (b).

using a Philips X'pert SW 3040 equipped by MRD lens and point Cu  $K_{\alpha 1}$ ,  $K_{\alpha 2}$  and  $K_{\beta}$  radiation source.

The dielectrical properties of the test and open structures were studied using HP8510C vector network analyser and a standard probe station S-1160 Signatone with microprobes (Fig. 1). The real, ReY, and imaginary, ImY, parts of complex admittance Y, of the structures were extracted directly from an inverted Smith chart. The capacitance C, conductivity G and effective loss tangent  $tan\delta$  were computed using Eqs. (1) and (2):

$$Y = ReY + ImY = G + j\omega C, (1)$$

$$tan\delta = ReY/ImY \tag{2}$$

where  $\omega$  is the angular frequency. In the measurements, the maximum level of microwave power delivered to the device under test is P=1 mW, and the amplitude of the microwave signal is estimated to be  $V_{ac}=\sqrt{2Z_0P}=0$ , 3V ( $Z_0=50$   $\Omega$  is the characteristic impedance of the transmission line), that is still low enough to cause substantial nonlinearities in the STO film. In measurements the dc bias V is reversed periodically to enable plots of the hysteresis effects in C-V performance. The tunability of test structure is defined as T(V)=[C(0)-C(V)]/C(0), where C(0) and C(V) are capacitances without and with dc bias, respectively.

#### 3. Results and discussion

#### 3.1. Microstructure

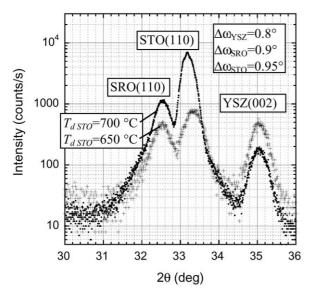

The normal XRD  $\theta$ -2 $\theta$  scans of SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/ CeO<sub>2</sub>/YSZ/Si heterostructures in the range of 20–120° reveal reflections associated only with SRO{110}, STO{110} and YSZ{001} families of planes. The CeO<sub>2</sub>{001} peaks are, probably, masked by STO{110} due to smaller thickness of CeO<sub>2</sub> layer.<sup>13</sup> Fig. 2 shows the  $30-36^{\circ}$  range  $\theta-2\theta$  scans of heterostructures obtained at different growth temperatures of  $SrTiO_3$  ( $T_d$  $_{\rm STO}$  = 650 and 700 °C). In order to identify the SRO and STO peaks, we compared the scans at different  $T_{\rm d\ STO}$ . As it can be seen, the increase of  $T_{\rm d}$  STO causes approximately a 10 times increase of intensity of the peak at  $2\theta \approx 33.2^{\circ}$ , which allows us to consider this peak as STO(110). The  $2\theta$ -position of YSZ(002) ( $2\theta \approx 35^{\circ}$ ) is in agreement with Refs. 10 and 13 and corresponds to the unstrained bulk lattice parameter (Table 1). Using the method of analysis of strained epitaxial film microstructure (Ref. 14) we calculated YSZ(002) position  $2\theta$  $\approx$ 36° for the coherent growth case. It indicates that YSZ grows incoherently on the Si substrate. The inset in Fig. 2 shows FWHM values of the  $\omega$  scans of YSZ, SRO, and STO layers for  $T_{\rm d~STO} = 700$  °C. The FWHM values of all layers are less than 1°, which indicates the good structural epitaxial growth.<sup>10</sup>

Fig. 2. The normal  $\theta$ – $2\theta$  XRD scans of SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ/Si heterostructures obtained at different growth temperatures of SrTiO<sub>3</sub> layer:  $T_{\rm d~STO}$  = 650 and 700 °C. The inset shows FWHM values of the  $\omega$  scans of YSZ, SRO, and STO layers for  $T_{\rm d~STO}$  = 700 °C.

### 3.2. Equivalent circuit

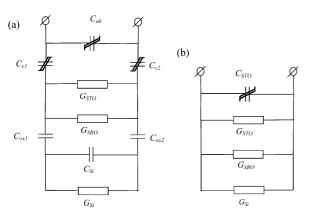

It is convenient to study the dielectric properties of the test structures using parallel equivalent circuits shown in Fig. 3(a). Here the capacitance between the electrodes due to the in-plane orientation of the STO film is denoted by  $C_{\rm ab}$ .  $C_{\rm C1}$  and  $C_{\rm C2}$  are the equivalent capacitances between the electrodes and SRO layer associated with the out-of-plane orientation of the STO film. The  $C_{\rm ox1}$  and  $C_{\rm ox2}$  capacitances are associated with CeO<sub>2</sub>/YSZ oxide layers between the SRO film and Si substrate. Due to shorting out by SrRuO<sub>3</sub> layer (sheet resistance  $\sim 50~\Omega/{\rm square})^{15}$  the static field does not penetrate the Si substrate. However, a time-varying field penetrates the SRO layer (skin depth  $\sim 5~\mu m$  at 1 GHz). We consider  $C_{Si}$  as the equivalent capacitance asso-

Fig. 3. Equivalent circuit of a SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ/Si test structure (a) and its simplified representation used for computational purposes (b).

ciated with the Si substrate, which is formed by time-varying fields and is independent of tuning dc bias. Thus, dc tuning of the capacitance of the test structure is caused only by the field-dependent dielectric permittivity of the STO layer. The conductances  $G_{\rm STO}$ ,  $G_{\rm SRO}$  and  $G_{Si}$  are associated with the real part of the loss in STO, SRO layers and Si substrate, respectively.  $G_{\rm STO}$  is determined by both the dc resistance due to the long range transport of charge carriers (the leakage current) and frequency-dependent resistance due to short range polarization (microwave loses), while  $G_{Si}$  value is determined only by microwave losses due to the isolation by  $CeO_2/YSZ$  oxides and due to shorting out by the SRO layer.

# 3.3. Dielectric properties

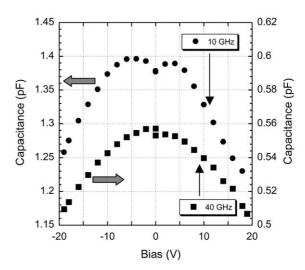

Fig. 4 presents the typical dc bias dependencies of the capacitance of a SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ test structure measured at 10 and 40 GHz. The dielectric permittivity of STO decrease under applied dc field resulting in a corresponding reduction in capacitance. The dependence of the dielectric permittivity of an incipient ferroelectric (SrTiO<sub>3</sub>) on the applied biasing field can be correctly modelled by solving the Ginsburg–Devonshire equation. <sup>16,17</sup>

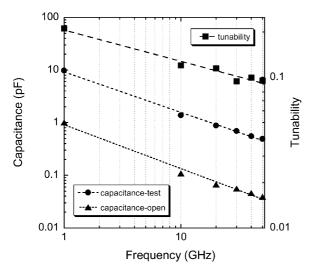

Fig. 5 shows the tunability (at 20 V) and zero bias capacitance of the SrTiO<sub>3</sub>/SrRuO<sub>3</sub>/CeO<sub>2</sub>/YSZ test structure and the capacitance of the corresponding CeO<sub>2</sub>/YSZ open structure versus frequency. As it can be seen from Fig. 5, the experimental capacitance of both structures in double-log format lie on the straight lines, i.e. dispersions correspond to the Curie–von Schweidler model:

$$\varepsilon = \varepsilon_{\infty} + k_0 \omega^{\alpha - 1},\tag{3}$$

Fig. 4. DC bias dependencies of the capacitance of a  $SrTiO_3/SrRuO_3/CeO_2/YSZ/Si$  test structure measured at 10 GHz and 40 GHz.

Fig. 5. Frequency dependencies of the tunability (at 20 V) and zero bias capacitance of the  $SrTiO_3/SrRuO_3/CeO_2/YSZ/Si$  test structure and  $CeO_2/YSZ/Si$  open structure.

where  $\varepsilon$  and  $\varepsilon_{\infty}$  are the real part of the permittivity and its value at very high frequencies, respectively;  $k_0$  and  $\alpha$  are parameters. Parameter  $\alpha$  is 0.23 and 0.17 for test and open structures, respectively. The capacitance of the test structure is at least 10 times larger then corresponding open structure in all frequency ranges. Hence, the capacitance of the test structure is determined mainly by permittivity of the STO layer.

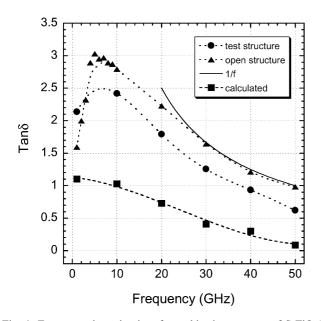

Fig. 6 shows zero bias loss tangents of the  $SrTiO_3/SrRuO_3/CeO_2/YSZ$  test structure and the corresponding  $CeO_2/YSZ$  open structure versus frequency. Due to the

Fig. 6. Frequency dependencies of zero bias loss tangent of  $SrTiO_3/SrRuO_3/CeO_2/YSZ/Si$  test structure,  $CeO_2/YSZ/Si$  open structure and values calculated for heterostructure excluding losses in Si substrate. The solid line presents a 1/f dependence.

screening effect of high permittivity of STO and SrRuO<sub>3</sub> films, the losses in test structure are smaller than that for the open structure. That total losses in the test structure are determined mainly by loss inside the Si substrate. The dielectric dispersion in the Si substrate is characterized by the dielectric (Maxwell) relaxation frequency<sup>19</sup>

$$f_{\rm dr} = 1/2\pi\tau_{Si} = 1/(2\pi \ \varepsilon_{Si} \ \varepsilon_0 \ \rho_{Si}),\tag{4}$$

where  $\tau_{\rm M}$  is the relaxation time,  $\varepsilon_{Si}$  and  $\varepsilon_0$  are the dielectric constants of silicon and free space, respectively,  $\rho_{Si}$  is resistivity of silicon. For our case  $\rho_{Si} = 25$   $\Omega$ cm and  $f_{\rm dr} \approx 6$  GHz, which exactly corresponds to the maximum losses of the open structure (Fig. 6). Besides, according to simple Drude model (Ref. 7), in the frequency range  $f >> f_{\rm dr}$  the loss tangent in silicon may be given as

$$\tan \delta_{Si} = 1/(2\pi f \varepsilon_{Si} \varepsilon_0 \rho_{Si}) = f_{dr} /f.$$

(5)

On Fig. 6 the solid line corresponds to  $\tan \delta_{Si} = G f_{\rm dr}/f$  (where G=10 is a geometrical factor). At frequencies above 30 GHz the 1/f relationship coincides with experimental curve, which also confirms that losses in open structure are mainly due to the Si substrate.

That capacitance of the open structure is much less than the capacitance of corresponding test structure (Fig. 5), which makes it possible to estimate the contribution of the losses due to the Si substrate. In the equivalent circuit [Fig. 3(a)] we can neglect the  $C_{\rm M}$  and  $C_{\rm ox1}$ ,  $C_{\rm ox2}$  forming the open structure capacitance. Fig. 3(b) shows the simplified equivalent circuit of the test structure. Here  $C_{\rm STO}$  combines the in-plane and out-off-plane capacitance of the STO film. In this case the loss tangent of the test structure is

$$\tan \delta_{\text{test}} \frac{\text{Re } Y_{\text{test}}}{\text{Im } Y_{\text{test}}} = \frac{G_{\text{STO}} + G_{\text{SRO}} + G_{\text{Si}}}{\omega \cdot C_{\text{STO}}}$$

(6)

where  $ReY_{test}$  and  $ImY_{test}$  are the real and imaginary parts of measured admittance, respectively. Then the loss tangent of structure without loss in Si substrate is

$$\tan \delta_{\text{test}} \frac{\text{Re} Y_{\text{test}} - \text{Re} Y_{\text{open}}}{\text{Im} Y_{\text{test}}} \tag{7}$$

where  $ReY_{\text{open}} = G_{Si}$  is real part of admittance of the open structure. The calculated values of  $\tan \delta$  are presented in Fig. 6. It can be seen that at frequencies up to 50 GHz the  $\tan \delta$  values go down to 0.08.

# 4. Conclusions

High quality  $SrTiO_3$  layers (FWHM=0.95°) with buffer  $SrRuO_3/CeO_2/YSZ$  thin film structure have been

grown on low-resistivity (25  $\Omega$  cm) Si(100) substrates using a laser ablation technique. The frequency dispersion of the SrTiO<sub>3</sub> dielectric constant is described by the Curie–von Schweidler model. The tunability of capacitance is larger than 10% and the calculated loss tangent (without losses in silicon) of 0.08 at 50 GHz makes this capacitor test structure promising for application in tunable microwave devices. The parasitic influence of the Si substrate in such devices can be cancelled by micromachining-forming a cavity in Si under the device,  $^8$  or increasing the conductivity and thickness of buffer SrRuO<sub>3</sub> layer in order to prevent the electric field penetration into the Si substrate.

## Acknowledgements

This work is supported by the SSF OXIDE program, The Swedish Research Council, and Chalmers Center for High Speed Technology.

#### References

- 1. Carlson, C. M., Rivkin, T. V., Parilla, P. A., Perkins, J. D., Ginley, D. S., Kozirev, A. B., Oshadchy, V. N. and Pavlov, A. S., Large dielectric constant ( $\varepsilon/\varepsilon_0 > 6000$ ) Ba<sub>0.4</sub>Sr<sub>0.6</sub>TiO<sub>3</sub> thin films for high performance microwave phase shifters. *Appl. Phys. Lett.*, 2000, **76**(14), 1920–1922.

- Petrov, P. K., Carlsson, E. F., Larsson, P., Friesel, M. and Ivanov, Z. G., Improved SrTiO<sub>3</sub> multilayers for microwave applications: growth and properties. *J. Appl. Phys*, 1998, 84(6), 3134–3140.

- Kim, W. J., Chang, W., Qadri, S. B., Pond, J. M., Kirchoefer, S. W., Chrisey, D. B. and Horwitz, J. S., Microwave properties of tetragonally distorted (Ba<sub>0.5</sub>Sr<sub>0.5</sub>)TiO<sub>3</sub> thin films. *Appl. Phys. Lett.*, 2000, **76**(9), 1185–1187.

- 4. York, R. A., Nagra, A. S., Periaswamy, P., Auciello, O., Streiffer, S. K. and Im, J., Synthesis and characterization of (Ba<sub>x</sub>Sr<sub>1-x</sub>) Ti<sub>1+y</sub>O<sub>3+z</sub> thin films and integration into microwave varactors and phase shifters. *Integrated ferroelectrics*, 2001, 34, 1617.

- 5. Chang, W., Horwitz, J. S., Carter, A. C., Pond, J. M., Kirchoe-

- fer, S. W., Gilmore, C. M. and Chrisey, D. B., The effect of annealing on the microwave properties of Ba<sub>0.5</sub>Sr<sub>0.5</sub>TiO<sub>3</sub> thin films. *Appl. Phys. Lett.*, 1999, **74**(7), 1033–1035.

- Zafar, S., Jones, R. E., Chu, P., White, B., Jiang, B., Taylor, D., Zurcher, P. and Gillepsie, S., Investigation of bulk and interfacial properties of Ba<sub>0.5</sub>Sr<sub>0.5</sub>TiO<sub>3</sub> thin film capacitors. *Appl. Phys. Lett.*, 1998, 72(22), 2820–2822.

- Abadei, S., Gevorgian, S., Cho, C.-R., Grishin, A. Low-frequency and microwave performances of laser-ablated epitaxial Na<sub>0.5</sub>K<sub>0.5</sub>NbO<sub>3</sub> films on high-resistivity SiO<sub>2</sub>/Si substrates. *J. Appl. Phys.* 91(4), 2267–76.

- Luo, H., Zhang, G., Carley, L. R. and Fedder, G. K., A post-CMOS micromachined lateral accelerometer. *J. Microelectromechanical Systems*, 2002, 11(3), 188–195.

- Jia, Q. X., Kung, H. H. and Wu, X. D., Microstructure properties of Ba<sub>0.5</sub>Sr<sub>0.5</sub>TiO<sub>3</sub> thin films on Si with conductive SrRuO<sub>3</sub> bottom electrodes. *Thin Solid Films*, 1997, 299, 115–118.

- Hou, S. Y., Kwo, J., Watts, R. K., Cheng, J.-Y. and Fork, D. K., Structure and properties of epitaxial Ba<sub>0.5</sub>Sr<sub>0.5</sub>TiO<sub>3</sub>/SrRuO<sub>3</sub>/ ZrO<sub>2</sub> heterostructure on Si grown by off-axis sputtering. *Appl. Phys. Lett.*, 1995, 67(10), 1387–1389.

- Jeon, Y.-A., Choi, E.-S., Seo, T.-S. and Yoon, S.-G., Improvements in tunability of (Ba<sub>0.5</sub>Sr<sub>0.5</sub>)TiO<sub>3</sub> thin films by use of metalorganic chemical vapor deposited (Ba,Sr)RuO<sub>3</sub> interfacial layers. *Appl. Phys. Lett.*, 2001, 79(7), 1012–1014.

- Mechin, L., Villegier, J.-C., Rolland, G. and Laugier, F., Double CeO2/YSZ buffer layer for the epitaxial growth of YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7-δ</sub> films on Si(001) substrates. *Physica C*, 1996, **269**, 124–130.

- Tian, Y. J., Linzen, S., Schmidl, F., Cihar, R. and Seidel, P., Large-area YBCO films for device fabrication. *Supercond. Sci. Technol.*, 1998, 11(1), 59–62.

- 14. Eom, C. B., Cava, R. J., Fleming, R. M., Phillips, J. M., van Dover, R. B., Marshall, J. H., Hsu, J. W. P., Krajewski, J. J. and Peck, W. F., Single-crystal epitaxial thin films of the isotropic metallic oxides Sr<sub>1-x</sub>Ca<sub>x</sub>RuO<sub>3</sub>(0≤x≤1). *Science*, 1992, 258, 1766–1769.

- Khamchane, K., Ivanov, Z. G., Rundqvist, P., Vorobiev, A. and Gevorgian, S., Correlation between resistivity and phase composition of epitaxial SrRuO<sub>3</sub> thin films. *Appl. Phys. Lett.* (submitted for publication).

- 16. Ginsburg, V. L., Zh. Eksp. Teor. Fiz, 1949, 19, 36.

- 17. Devonshire, A. F., Philos. Mag, 1949, 40, 1040.

- Jonscher, A. K., Universal Relaxation Law. Dielectric Relaxation in Solids. Chelsea Dielectric Press, London, 1996.

- Balanis, C. A., Advanced Engineering Electromagnetics. John Wiley & Sons, New York, 1989.